これはM3のときに書こうと思って、時期を逸してしまった話。

AppleのiPad Proと内蔵のM4チップが発表されました。

M4はトランジスタ数で28billion(280億)個ということで、相当大きそうなチップです。intelのi9のトランジスタ数に比べても3~5倍多いらしいです。それだけ大きいと歩留まりが問題になってきます。ウエハにはある程度の密度の欠陥が避けられず、チップが大きくなればなるほど1つのチップに欠陥が当たる率が増え、結果的に捨てるチップの割合が高くなるからです。

性能上の限界も製造ロットごとにばらつきます。インテルのCPUなどは、クロックスピードにいくつかバリエーションを設けて、速いチップはより高く売るというようなことをしています。あれはプロセスを変えているという部分もあるかもしれませんが、基本的には同じ設計で作ってから選別しているはずです。

Appleの場合はスピードのバリエーションは作っていませんが、CPU数にバリエーションがあります。

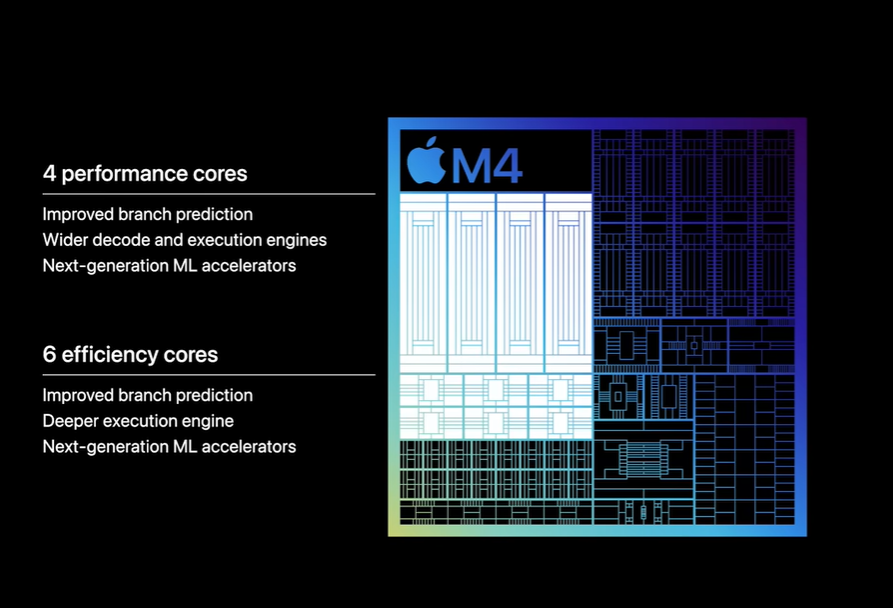

これはiPad Proのページから抜き出したものですが、ストレージが256GB/512GBのモデルは「3つの高性能コアと6つの高効率コア」、1TB/2TBモデルは「4つの高性能コアと6つの高効率コア」となっています。高性能コアの数が1つ違って、外は同じです。これはどういうことか。設計上は別々に作るのではなく、同じ設計であるはずです。別々に設計するのであれば、コアの数が1つ違うだけというようなことはせず、もっと仕様のバリエーションがあちこちにつくはずです。ということは、ここで選別が行われているということです。チップの欠陥が高性能コアのうちのどれかに当たれば、そのコアの動作を止めて残りの3つを動作させれば、「3つの高性能コア」のバージョンができるということです。

これはAppleが発表しているチップ(ダイ)の絵で、白い表示のエリアの大部分が高性能コアの領域です。仮にこれが占める面積がチップの20%であったとすると、おおざっぱな計算でいうとウエハの欠陥によるチップの不良品のうち、約20%が「3つの高性能コア」バージョンとして救えるということになります。仮に全部を「4つの高性能コア」にする場合の歩留まりが80%であったとすると(チップが大きいのでそれなりに歩留まりは低いはず)、84%ぐらいまで歩留まりが上げられることになります。結果的に原価も抑えることができます。intelはこれをやっていないのかと思っていたのですが、intelのMPUも最近のi9などを見るとコア/スレッド数にバリエーションが付いてました。

さらに考えると、製品の上位バージョンと下位バージョンの割合は価格でコントロールするだけなので、思うようにはなりません。下位バージョン(3コア品)の販売が半分だったとすると、4コア動作するチップのうち1つの機能を殺して製品に使うことになるわけです。もったいない気もしますが、別々に設計製造するコストにくらべれば、その方が効率が良いのでしょう。

なんとも残念な気がしますし、もったいないからそれ生かしといてよと言いたくなりますが、多分そういうことです。せっかく性能が出ているのにそれを殺して出荷するという例は外にもあるでしょうか。

0 件のコメント:

コメントを投稿